이미지 확대보기

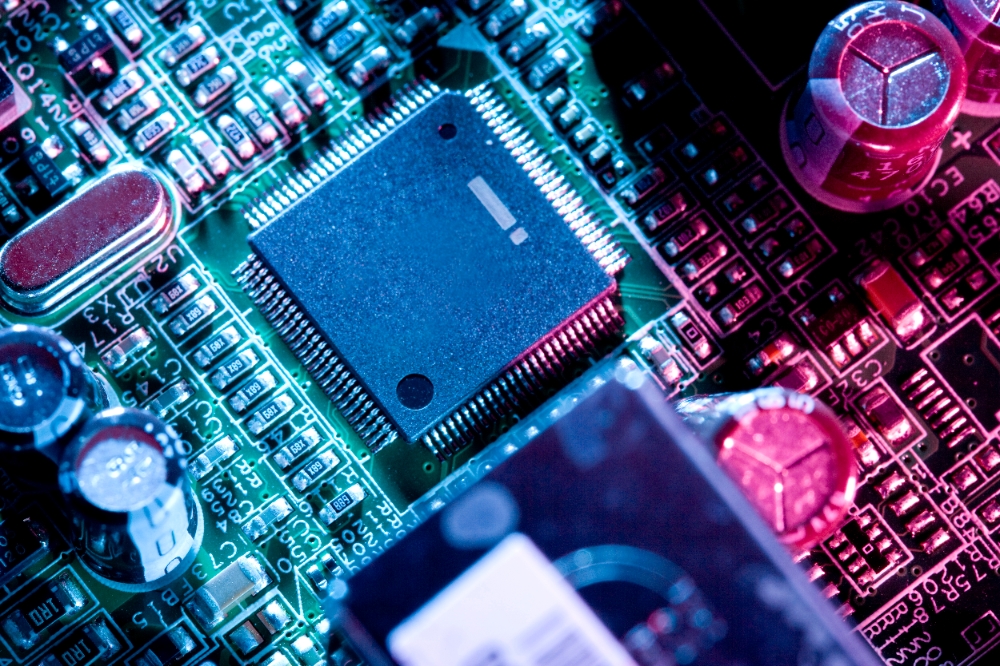

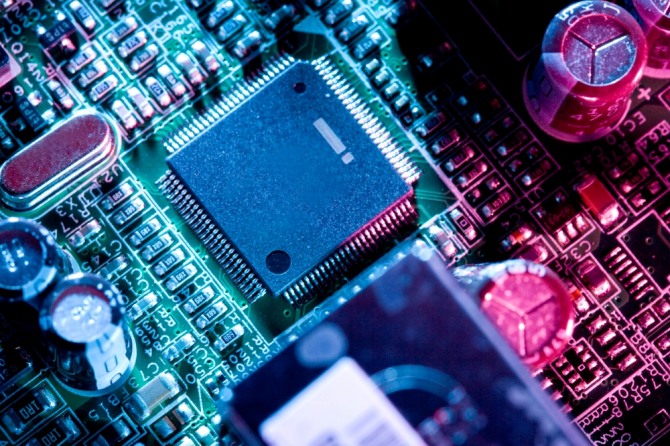

이미지 확대보기테크인사이트의 최근 보고서에 따르면 SMIC는 ASML의 최첨단 EUV 리소그래피 기계를 사용하지 않고도 7나노 칩을 만들고 비트코인 채굴 프로세서를 공급했다고 한다.

우리가 몰랐던 잘 알려지지 않은 사실은 ASML의 EUV 리소그래피 기계가 7나노 칩을 생산하기 위한 유일한 옵션이 아니라는 것이다. 이 기계가 등장하기 전에 TSMC와 삼성을 비롯한 세계 유수의 칩 파운드리는 포토리소그래피 기계를 사용하여 7nm 칩을 생산하고 있었다.

ASML의 EUV 리소그래피 기계가 도입되기 몇 년 전에 주조 공장은 각 칩에 에칭하는 데 필요한 홈보다 훨씬 큰 193S나노 파장의 광리소그래피를 사용해야 했다. 그러나 칩의 발전이 이 리소그래피 시스템의 한계인 80나노에 가까워짐에 따라 칩 제조업체는 보다 현대적인 EUV 리소그래피 기계가 등장할 때까지 트랜지스터 소형화 등 이 시스템을 활용한 다양한 솔루션을 찾았다.

그러나 더 작은 22나노 공정에서 칩 제조업체는 새로운 장애물에 직면했다. 이 프로세스의 과도한 트랜지스터 밀도는 포토리소그래피가 단일 인쇄에서 충분히 정확한 라인을 생성하는 것을 불가능하게 만들었다.

웨이퍼의 홈 품질을 개선하기 위해 칩 제조업체는 이중 패터닝 리소그래피 또는 이중 패터닝 리소그래피를 고려했다.

칩 리소그래피 공정은 이제 Litho-etch-litho-etc(LELE)의 네 가지 주요 단계로 나뉜다. 이 솔루션을 사용하면 칩 패턴 각 레이어가 이전과 같이 단일 패스로 인쇄되는 대신 트랜지스터 밀도가 낮은 2개의 레이아웃 레이어로 분할된다.

이 두 구성 레이어는 각각 두 개의 개별 인쇄 및 조각 프로세스로 구성되어 두 개의 거친 패턴을 형성한다. 그런 다음 웨이퍼에 더 미세한 선과 더 좁은 간격을 가진 패턴을 형성하기 위해 결합 및 적층된다.

또 다른 중요한 부분은 칩 제조업체가 원래 패턴을 포토리소그래피를 위한 최적의 패턴 레이어로 분해하는 데 도움이 되는 칩 설계 소프트웨어다.

45나노 공정에서 빛 파장의 한계를 극복하기 위한 다중 패턴 리소그래피 솔루션과 동시에 칩 제조업체는 평면 칩 설계에서 FinFET를 사용하는 3차원 칩으로 이동하기 시작했다. 이를 통해 칩 제조업체는 트랜지스터 간격을 과도하게 줄이지 않고도 트랜지스터 밀도를 계속 높일 수 있다.

듀얼 패턴 리소그래피를 통해 칩 제조업체는 트랜지스터의 기술 발전을 40나노에서 14나노로 30% 더 줄일 수 있다.

그러나 칩 기술이 10나노 이하(예: 7nm)에 가까워지고 EUV 리소그래피 시리즈가 아직 출시되지 않은 경우 칩 제조업체는 제조 솔루션과 함께 이전 시리즈를 계속 활용해야 한다.

반도체 제조사들은 트리플 패터닝 솔루션에 의지했다. 칩 생산 단계는 각 패턴 레이어에 대해 3배의 리소그래피(LELELE)로 더욱 확장된다.

듀얼 패턴 솔루션으로 이미 복잡했던 칩 제조는 이제 3패턴 리소그래피로 더욱 복잡해진다. 칩 설계를 수정해야 했고 칩 제조 소프트웨어 도구를 다시 설계해야 했다.

원래 칩 디자인을 2개의 패턴으로 분할하는 것보다 3개의 최적 패턴으로 분해하는 것이 훨씬 더 어렵다. 칩 제조 공정은 이전보다 훨씬 더 복잡하고 길어졌다.

그러나 이 솔루션은 TSMC 및 삼성과 같은 칩 제조업체가 2018년에 출시된 애플의 A12 바이오닉(Bionic) 칩이 칩셋의 첫 번째 라인인 DUV 리소그래피를 사용하여 7나노 칩을 생산하는 최초의 회사가 되는 데 도움이 되었다.

TSMC의 7나노 칩 공정을 적용한 최초의 프로세서다. 따라서 SMIC가 이제 ASML의 EUV 리소그래피 기계 없이도 7nm 칩을 생산할 수 있다는 것은 놀라운 일이 아니다.

◇

문제는 없나? 비용과 제작 기간

45/40나노 공정에서 각 칩의 디자인은 40개의 서로 다른 마스크 레이어로 나뉜다. 14나노 및 10나노 공정의 경우 칩 마스크의 수는 최대 60층이다. 7나노 공정에서도 각 칩 디자인의 마스크 수는 최대 80개 또는 85개 레이어가 될 수 있다. 더 많은 마스킹 레이어는 더 높은 비용을 의미한다.

또한 칩 생산 시간도 길어진다. 이전에는 마스크 레이어를 처리하는 데 1~1.5일이 걸렸지만 7나노 다중 패턴 리소그래피를 사용하면 칩 제조업체가 완성된 웨이퍼를 배송하는 데 최대 5개월이 걸린다.

문제는 마스크 수가 증가할 뿐만 아니라 웨이퍼 표면 코팅량도 증가한다는 점이다. 코팅이 많을수록 제조 공정 중에 트랜지스터 극을 정렬하기가 더 어렵다. 이로 인해 칩 제조 프로세스가 더 오류가 발생하기 쉽다.

ASML의 EUV 리소그래피 기계는 칩 산업에 거대한 전환점이었다. 이상의 문제점을 해결한 것이다. DUV 리소그래피의 193나노 파장보다 훨씬 짧은 13.5나노의 매우 짧은 파장으로 칩 산업이 직면한 문제를 해결했다.

더 짧은 파장은 ASML의 엔진이 더 적은 수의 패턴 레이어를 가진 리소그래피 칩을 가능하게 하지만 칩 프로세스가 5나노로 감소된 경우에도 여전히 더 나은 품질을 제공한다. 적은 수의 모델은 칩 생산 시간과 비용을 줄이는 동시에 칩 고장률을 줄이고 칩 생산 생산성을 높인다. 경쟁력 제고 효과다.

그러나 SMIC는 이 혁명의 결실을 누리지 못한다. 고급 EUV 리소그래피에 액세스할 수 없으면 복잡, 높은 비용 및 낮은 생산성에 시달려야 한다.

7나노 칩을 생산하기 위해 DUV 리소그래피 기계에 의존해야 한다.

이것은 SMIC의 7나노 칩이 비트코인 채굴 컴퓨터의 프로세서에만 적용되는 이유를 설명할 수 있다. 비트코인 마이닝 칩은 간단하며 그다지 중요하지 않은 영역에만 적용할 수 있다.

한편, 어느 때보다 더 많은 하이테크 칩에 굶주린 중국의 거대 기술 기업 화웨이는 아직 SMIC의 제품을 사용할 기미를 보이지 않고 있다.

더 싼 가격으로 하자가 없는 칩을 사용하는 것이 고도화된 전자제품을 고장 없이 가동하게 한다. 가격 경쟁력과 시간의 싸움에서 이기지 못하는 제품이 시장에서 살아남기는 쉽지 않다.

중국의 기술 개발에 대한 열정은 높이 사지만 아직 최고의 기술에 진입한 것은 아니다. 시장의 일정 분야, 그것도 중국 내수시장에서 통용되는 기술 단계로 보인다. 다만, 중국의 노력을 목도하면서 더 긴장해야 한다.

박정한 글로벌이코노믹 기자 park@g-enews.com