칩 표면에 '미세 유로' 직접 형성…열전달물질(TIM) 병목 뚫고 열 저항 30% 낮춰

엔비디아 '블랙웰 울트라'(1400W) 거뜬…'TDP 5000W' 시대 AI 서버 발열 문제 해결

엔비디아 '블랙웰 울트라'(1400W) 거뜬…'TDP 5000W' 시대 AI 서버 발열 문제 해결

이미지 확대보기

이미지 확대보기인공지능(AI) 시대의 심장인 GPU(이미지 처리 반도체)가 뜨거운 발열과의 전쟁을 치르고 있다. AI 서버의 성능이 기하급수적으로 치솟으며, '열을 어떻게 잡느냐'가 반도체 기술 경쟁의 핵심으로 떠올랐다. 이 격전의 중심에서, 세계 최대 파운드리(반도체 위탁생산) 기업인 TSMC가 칩(SoC)에 직접 '물길'을 내는 대담한 방식의 차세대 냉각 기술을 선보여 업계의 이목을 집중시키고 있다고 닛케이가 30일(현지시각) 보도했다. 2025년 10월 현재, 이 기술은 차세대 AI GPU의 극한 발열 문제에 대응하며 기존 냉각 방식의 근본적 전환을 예고하고 있다.

'열 저항 병목' TIM 제거, 칩 표면에 길을 내다

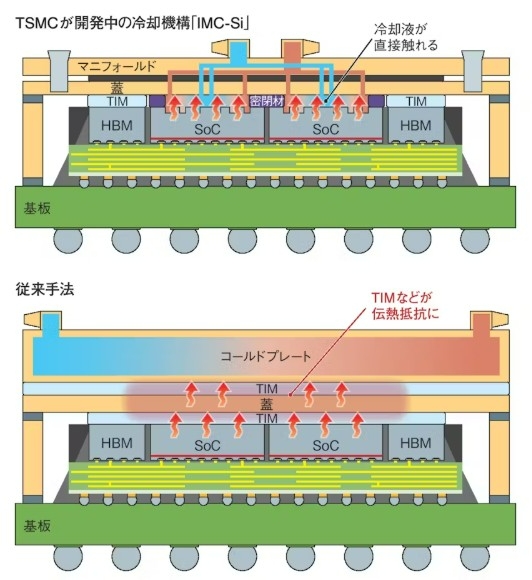

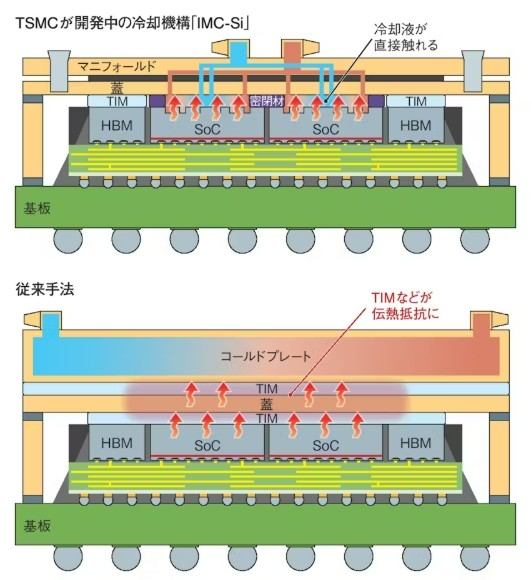

TSMC가 개발에 총력을 기울이는 이 기술은 'Si-integrated micro cooler(IMC-Si)'다. 반도체 칩 표면에 냉각수가 흐르는 미세한 유로(마이크로채널)를 직접 형성, 칩을 액체로 식히는 방식이다.

기존에는 '콜드 플레이트'라는 부재를 칩 위에 얹어 냉각했다. 하지만 이 방식은 칩과 콜드 플레이트 사이에 열전달 물질(TIM)을 반드시 삽입해야 했고, 이 TIM이 성능 저하의 핵심 병목(bottleneck)으로 작용해 열의 흐름을 방해하며 냉각 효율을 떨어뜨리는 요인으로 작용했다.

첨단 패키징 'CoWoS-R'과 결합

TSMC는 지난 5월 미국에서 열린 반도체 실장 기술 국제 학회(ECTC)에서, 자사의 최첨단 패키징 기술인 'CoWoS-R'에 이 냉각 구조를 성공적으로 결합했다고 발표했다.

CoWoS-R은 유기 인터포저 기반 다칩 집적 패키지 기술로, AI 서버 등 고성능 컴퓨터용 핵심 기술이다. TSMC 측은 "CoWoS-R 공정에 최소한의 변경을 가하는 것만으로 충분하다"고 설명했다.

구체적인 공정은 이렇다. 먼저 유기 인터포저에 칩을 실장한 뒤, 칩 표면에 '마이크로 필러 어레이'라는 미세한 요철을 지그재그 형태로 촘촘히 형성한다. 이 요철은 냉각수와 칩 표면의 접촉면을 최대화해 냉각 효율을 높이는 핵심 역할을 한다. 요철 형성 후에는 냉각 필름을 덮어 이물질이나 오염 유입을 차단한다.

이후 기존 CoWoS 공정과 동일하게 상하를 반전시켜 'C4' 범프를 형성하고, 다시 뒤집어 패키지 기판에 실장한다. 마지막으로 칩 주변을 밀봉재로 감싸고 뚜껑을 덮어 마무리하는 봉지(封止) 공정을 거친다.

3400W 방열 성공…'블랙웰 울트라' 발열도 제압

시뮬레이션 결과, 성능은 강력했다. 40도의 순수(純水)를 분당 10리터씩 흘려보낼 경우, IMC-Si가 적용된 패키지는 약 3400와트(W)의 열을 흡수(방열)하는 것으로 나타났다.

이 수치는 현존 최고 사양 GPU 중 하나로 꼽히는 엔비디아의 최신 '블랙웰 울트라'(최대 설계 전력 1400W)도 거뜬히 감당하며, 앞으로 더욱 높아질 칩의 소비전력(TDP) 증가에도 충분히 대응할 수 있는 수준이다.

상용화의 관건인 신뢰성 또한 검증을 마쳤다. 패키지 내부에 유로를 만든 전례가 없어 표준 평가 방법이 부재한 상황에서, TSMC는 데이터센터 업계 표준 단체인 '오픈 컴퓨트 프로젝트(OCP)'의 지침을 준용했다.

구체적으로 물보다 분자가 작은 헬륨 가스를 이용해 극한의 조건(260도 리플로 공정 3회, 영하 40도~125도 온도 사이클 2000회, 150도 고온 1000시간 노출, 150도 액체 1000시간 침수 등)에서 누출 테스트를 진행했다. 그 결과, 모든 조건에서 합격 기준치에 비해 한 자릿수나 더 낮은 누출률을 기록하며 안정성을 입증했다.

'TDP 5000W 시대' 겨냥한 열관리 혁신

이번 기술 개발은 차세대 AI 칩의 집적도가 급상승하며 기존 공랭식이나 일반 액체 냉각 방식이 한계에 부딪혔다는 배경에서 출발한다.

업계에서는 '칩레벨 액체 냉각(Chip-level liquid cooling)'이 앞으로 반도체 공정·패키징·설계가 동시에 최적화되는 'DTCO/STCO(공정-기술-구조 동시최적화)'의 핵심 영역으로 부상할 것으로 보고 있다.

TSMC는 이번 IMC-Si 기술을 통해 칩 설계 단계부터 냉각 효율을 내재화하는 '열관리 혁신'을 주도하며, 엔비디아, AMD 등이 주도하는 차세대 AI 가속기 시장에서 확고한 기술 주도권을 확보한다는 전략이다.

앞으로 과제는 마이크로채널 유로의 형상을 최적화하고, 패키지 변형(휨)이나 봉지 공정의 신뢰성을 더욱 높이는 것이다. 또한 OCP 신뢰성 지침과 같은 업계 표준 인증 체계 구축도 병행하고 있다.

TSMC의 IMC-Si 기술은 앞으로 도래할 'TDP 3000~5000W' 시대의 발열 한계를 극복하고, AI 인프라 발전의 핵심 기반이 될 전망이다. 아울러 블랙웰 울트라 같은 최고 성능 GPU의 안정적 구동을 넘어, 데이터센터 전체의 냉각 구조 혁신에도 중대한 영향을 미칠 것으로 보인다.

박정한 글로벌이코노믹 기자 park@g-enews.com