이미지 확대보기

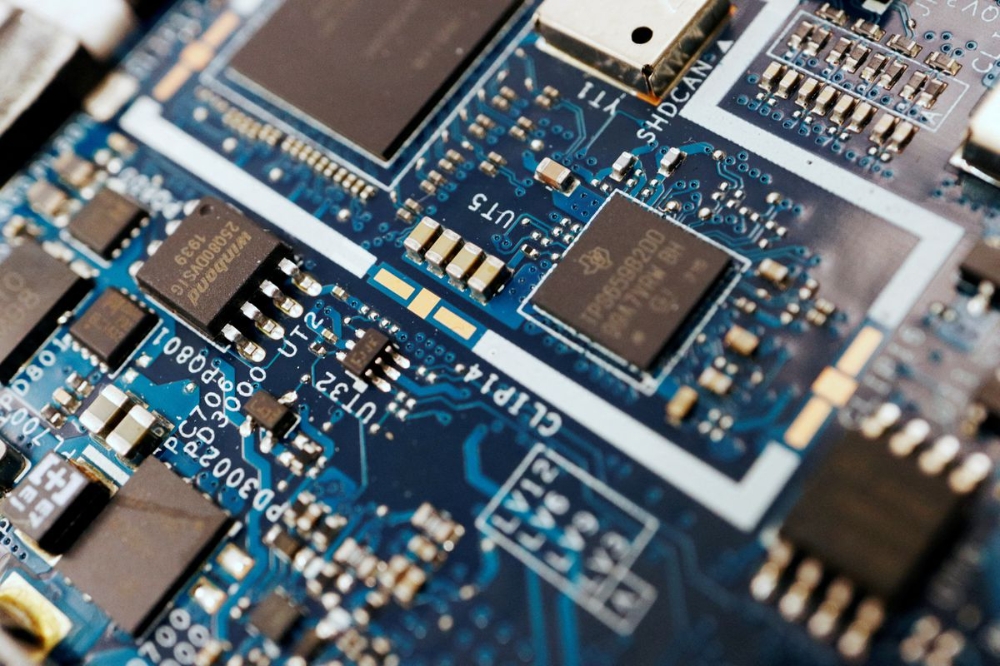

이미지 확대보기탐스 하드웨어가 국제 비즈니스 전략(International Business Strategies, IBS) 자료를 인용해 2nm급 칩 설계 비용이 총 7억 2500만 달러가 소요될 것으로 추정된다고 1일(현지시간) 보도했다.

이처럼 큰 비용이 투입되는 것은 트랜지스터 크기는 작아지면서 칩 성능과 전력 효율이 향상되는 것을 구현하기 위한 설계와 제조가 더 어려워지고 매우 복잡해 많은 자원이 필요하기 때문에 비용도 상승했기 때문이다.

칩 설계 비용이 급등하기 시작한 것은 2014년 FinFET 트랜지스터가 도입되면서부터였다. 그 이전에는 트랜지스터가 평면 구조로 되어 있었다. FinFET 트랜지스터는 트랜지스터의 모양을 삼각형으로 바꾸어, 칩 성능과 전력 효율을 향상했다. 이를 구현하기 위한 칩 설계가 복잡해지고, 제조를 위해서는 첨단 공정 기술이 필요했다.

일반적으로 칩 설계 개발 비용에서는 소프트웨어 개발 및 검증이 칩 설계 개발 비용의 가장 큰 부분을 차지한다. 소프트웨어의 경우 약 3억 1400만 달러, 검증의 경우 약 1억 5400만 달러가 소요된다.

칩 설계에는 하드웨어 설계와 소프트웨어 개발이 모두 필요하다. 하드웨어 설계는 칩의 물리적 구조를 설계하는 것이고, 소프트웨어 개발은 칩의 동작을 제어하는 프로그램을 개발하는 것이다. 검증은 칩이 설계대로 작동하는지 확인하는 과정이다.

칩이 고도화되면서 기능이 복잡해지고 있다. 따라서, 칩을 제어하는 소프트웨어도 복잡해지고, 성능과 전력 효율을 향상하는 소프트웨어도 최적화해야 한다. 칩의 설계 오류를 발견하고 수정하기 위해 검증도 더 세밀하고 철저히 해야 한다. 이것이 모두 비용으로 연결된다.

◇ 최첨단 칩 설계 독점구도 해결 시급

칩 설계 비용이 증가할 것이라는 데는 논쟁의 여지가 없지만, IBS 추정치가 너무 과하다는 비판도 있다.

스타트업 등 소규모 개발업자들은 독점 구도를 깨야 비용 상승을 막을 수 있다고 주장하고 정부 차원의 정책 개입을 요구한다.

정부가 이를 방치하면 첨단 칩 설계는 대기업에서만 할 수 있고, 결국 독점구도는 소비자 부담 비용을 늘릴 것이라고 주장한다. 대기업이 독점하면 신생 기업의 진입이 어려워지고, 혁신적인 기술 개발이 저해될 수 있다고 말한다.

이들은 2nm급 칩 설계 비용이 총 7억 2500만 달러가 소요된다는 추정은 최대치 혹은 상한선이라고 말한다.

이 칩을 개발하려는 회사가 관련 지적 재산권이 없이 모든 것을 처음부터 개발해야 한다는 가정하에 추정한 것으로 IBS 추정치는 2nm 칩 설계에 최고 상한선을 말한 것이 된다는 것이다.

지적 재산권은 설계자와 라이선스 계약을 통해 구입할 수 있어 설계 시간을 단축하고 비용 절약을 할 수 있으며, 칩 크기도 일정 수준을 유지하면 설계와 제조 비용을 줄일 수 있다고 말한다.

이들은 칩 설계 비용이 너무 비싸지면서 스타트업은 칩 개발에 필요 자원을 확보하기가 어려워졌고, 대기업들은 이미 많은 지적 재산권과 자원을 보유하고 있어, 스타트업보다 빠르고 저렴하게 칩을 개발할 수 있다고 주장한다.

이런 추세가 계속되면 반도체 산업은 경쟁이 제한되고, 독점이 심화되어 소비자의 선택권도 줄어들 수 있다고 경고한다. 이 때문에 독점을 깨는 정책 구사가 필요하다고 말한다.

이들은 첨단 칩 제조의 비용을 줄이기 위한 대안으로 칩 설계 교육 및 인력 양성, 칩 설계 지원 확대, 칩 설계 인프라 구축, 칩 설계 소프트웨어의 오픈소스화, 칩 설계 소프트웨어의 공동 개발을 제안한다.

또한, 스타트업 관계자들은 칩 설계 지적 재산권 공유 플랫폼 구축, 칩 설계 지적 재산권 라이선스 비용 지원, AI 지원 전자 설계 자동화 도구 보급 등도 독점을 해소하고 비용을 절감하는 데 도움이 될 것이고 말한다.

이들은 스타트업 생태계를 보호 육성해야 경쟁을 촉진해 혁신을 창출하고, 소비자 선택권을 확대할 수 있으며, 일자리 창출로 경제 성장도 도모할 수 있다고 말한다.

박정한 글로벌이코노믹 기자 park@g-enews.com