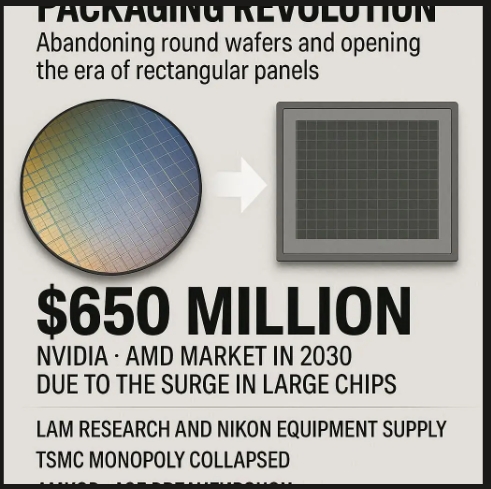

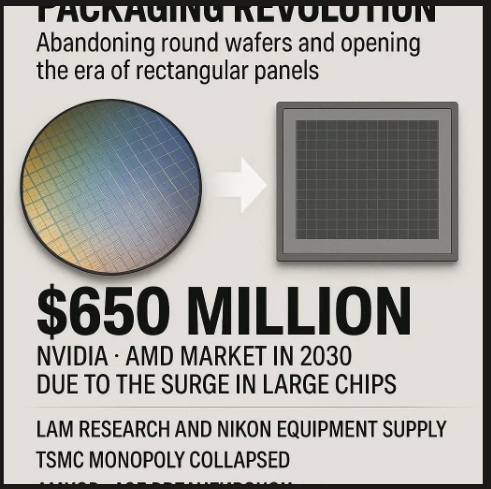

엔비디아·AMD 대형 칩 급증에 2030년 시장 6억 5000만 달러...램리서치·니콘 장비 공급, TSMC 독점 무너지고 앰코·ASE 약진

이미지 확대보기

이미지 확대보기전자전문매체 EE타임스는 지난 16일(현지시간) 램리서치와 니콘 등 반도체 장비업체들이 패널 생산용 첨단 패키징 장비를 공급하며 이르면 2027년부터 본격 시장이 열릴 것이라고 보도했다.

엔비디아 블랙웰, 원형 웨이퍼 한계 드러내

AI 칩이 커지면서 반도체 제조 장비의 최대 레티클(노광 면적) 크기를 넘는 사례가 늘고 있다. 엔비디아 AI 칩 블랙웰은 약 800㎟ 크기 칩 두 개를 결합한 두 레티클 패키지 구조다. 시장조사업체 ACM리서치에 따르면 이 크기 칩은 지름 300㎜ 원형 웨이퍼 하나에 약 64개를 만들 수 있으나, 정사각형 칩을 원형 웨이퍼에 놓으면 상당량 실리콘이 낭비된다.

실리콘 웨이퍼가 원형인 이유는 원통형 실리콘 잉곳(덩어리)을 잘라 만들기 때문이다. 마치 양초를 만들 때 녹인 밀랍을 담그는 과정처럼 오래된 방식이다.

램리서치 치핑 리 전무는 EE타임스에 "레티클 크기가 4500㎟에 이르는 수년 안에 패널 방식으로 바뀌는 전환점이 올 것"이라며 "2030년쯤 레티클 크기가 7700㎟를 넘으면 패널이 AI 칩을 만드는 중간 연결판(인터포저)으로 훨씬 좋은 선택이 될 것"이라고 말했다.

패널 방식 시장, 해마다 평균 27% 고속 성장

시장조사업체 욜그룹이 올해 3월 발표한 보고서를 보면 현재 인쇄회로기판(PCB)과 평판디스플레이 생산을 돕는 패널 레벨 패키징(PLP) 시장은 지난해 1억 6000만 달러(약 2280억 원)에서 2030년 6억 5000만 달러(약 9260억 원) 규모로 커질 전망이다. 고성능 컴퓨팅(HPC)과 AI 수요가 주요 성장 동력이다.

욜그룹은 PLP 시장이 2024년부터 2030년까지 해마다 평균 27% 성장할 것으로 내다봤다. 삼성전자와 세계 최대 반도체 패키징 업체 ASE 등 기존 업체는 물론 앰코, 일본 스타트업 파운드리 라피더스, 심지어 TSMC도 3년 안에 고급 팬아웃 패키징 기술을 선보일 계획이라고 이 보고서는 전했다.

램리서치는 300㎜에서 600㎜에 이르는 패널 위에서 칩들을 연결하는 배선 기술(인터커넥트)을 개발해 왔다. 리 전무는 "패널에서 패키징 구조를 만들면 300㎜에서 멈출 필요가 없고 600㎜까지 키울 수 있다"며 "한 패널에 더 많은 칩을 올리고 한 시스템에서 처리할 수 있다"고 설명했다.

한편 미국 정부는 신규 패널 공급업체 육성에 나섰다. 한국 기업 SKC 계열사인 유리 기판 제조사 앱솔릭스(Absolics)는 지난해 5월 미국 정부에서 반도체법(CHIPS Act) 지원금 7500만 달러(약 1060억 원)를 받아 미국 조지아주에 기판 시설을 짓는다고 발표했다. 당시 앱솔릭스는 자사 유리 기판이 AI·HPC·데이터센터용 칩 성능을 높일 것이라고 밝혔다.

OSAT 업체들, 첨단 패키징 시장 뛰어든다

칩을 주거용 건물처럼 층층이 쌓는 2.5차원(D)과 3D 수준 첨단 패키징은 그동안 고비용 클린룸 시설을 가진 파운드리 TSMC가 독점했다. 그러나 ASE와 앰코 같은 반도체 조립·테스트 외주업체(OSAT)들이 첨단 시설 투자를 늘리면서 판이 바뀌고 있다.

세계 2위 칩 패키징 업체 앰코는 지난달 7일 미국 애리조나주 투자 규모를 70억 달러(약 9조 9700억 원)로 처음 계획보다 3배 넘게 키운다고 발표했다. TSMC와 인텔 대형 팹 프로젝트와 가까운 이 새 시설은 2028년 초 가동을 시작하며 75만㎡가 넘는 클린룸 공간을 확보한다.

앰코는 EE타임스에 보낸 이메일 성명에서 "2023년 계획을 발표한 뒤 연방과 주 정부 기관, 공급망 파트너, 고객들과 긴밀히 협력하고 있다"며 "2028년 초 전면 가동 일정을 지키고 있으며 이는 이 규모 첨단 제조 역량을 만드는 복잡한 특성을 반영한 것"이라고 밝혔다.

리 전무는 "첨단 패키징이 대형과 중견 OSAT 업체를 포함해 더 많은 업계 참여자한테 폭넓게 쓰인다"며 "일부 OSAT는 이를 가치 사슬을 올라가는 방법으로 보고 있고, 대형 업체들이 이를 실현할 수 있을 것"이라고 말했다.

2027년 본격 상용화...새 생태계 만든다

장비업체들도 패널 시장 진출에 나섰다. 니콘은 지난 7월 최대 600㎜ 크기 대형 기판을 돕는 첨단 패키징용 디지털 리소그래피 시스템 DSP-100 주문 접수를 시작했다. 니콘은 자사 웹사이트에서 "100㎟ 대형 패키지는 300㎜ 웨이퍼를 쓸 때보다 기판당 생산성이 9배 높다"며 "마스크리스 기술로 생산 비용을 줄이고 솔리드스테이트 광원으로 유지보수 비용을 낮춰 친환경 제조를 돕는다"고 설명했다.

어플라이드머티어리얼즈 아물리아 아타예이드 이종통합사업부 전략마케팅 수석이사는 EE타임스에 "실리콘은 좋은 기판 재료이나 웨이퍼가 원형이라 기판당 네모난 AI 가속기를 조금밖에 못 만든다"며 "평판 디스플레이용 대형 기판을 다룬 경험을 바탕으로 어플라이드는 웨이퍼 공정 기술을 패널 규모로 키울 수 있는 독특한 위치에 있다"고 말했다.

램리서치는 지난 9월 여러 칩을 3차원으로 쌓고 다른 종류 칩들을 고밀도로 합치는 티오스(Teos) 3D 장비를 선보였다. 회사 쪽은 이 장비가 칩 사이 빈틈을 매우 두껍고 고르게 메우고, 절연막을 쌓는 기술을 혁신했으며, 향상된 감시 기술을 갖췄다고 밝혔다.

리 전무는 "최종 생태계가 어떤 모습일지는 아직 불확실하다"며 "여러 크기가 다양한 업체에서 나오고 있고 표준이 부족하나 멀리 보면 표준을 만들 것"이라고 말했다. 업계에서는 패널이 현재 저가형 칩과 무선주파수(RF) 칩을 위해 소량 생산하나 AI 칩용은 아직 개발 단계이며 시간이 걸릴 것으로 보고 있다.

박정한 글로벌이코노믹 기자 park@g-enews.com

![[뉴욕증시] 3대 지수, 예상 밑돈 물가에 상승](https://nimage.g-enews.com/phpwas/restmb_setimgmake.php?w=270&h=173&m=1&simg=2025102506355401024c35228d2f5175193150103.jpg)