이미지 확대보기

이미지 확대보기3나노 칩은 5나노 칩에 비해 전력 절감, 성능 향상, 면적 축소 효과를 기대할 수 있다. 최첨단 사양의 스마트폰이나 PC, 데이터센터를 구축하려는 글로벌 기술기업들은 매수 여부를 적극 검토 중인 것으로 알려졌다.

3나노 칩 개발에 막대한 비용이 투입되어 그 상승분만큼을 전자기기 제조 기업들이 제품 가격에 전가할 경우 소비자 부담으로 이어져 매출이 감소할 수 있어서다.

이에 글로벌 초대형 전자기기 구매 기업들인 애플, 퀄컴, 엔비디아, AMD 등이 3나노 칩 구매에 다소 신중한 입장을 보이고 있는 것으로 알려졌다.

◇

3나노 칩의 성능 비교

3나노 칩은 5나노 칩에 비해 최대 45% 전력 절감, 23% 성능 향상, 16% 면적 축소 효과가 있다.

3나노의 경우 연구개발(R&D) 공정에 50억 달러, 생산라인 비용 200억 달러 등 총 250억 달러가 투자된다. 1세대 3나노의 1개당 생산단가는 공정 개선에도 불구하고 트랜지스터 1개당 비용이 2배로 늘어나는데 성능은 11% 개선에 불과하다.

이런 이유로 3나노는 5나노, 7나노에 비해 칩 비용 부담이 너무 크다는 것이다. 5나노는 웨이퍼당 1만6000달러, 3나노의 경우 2만 달러로 가격이 25% 상승했다. 2023년에는 물가 상승으로 비용이 더 오를 수 있다.

3나노 웨이퍼를 구매할 경우 애플이나 퀄컴 등에서 판매하는 하드웨어 가격 역시 그만큼 비싸진다. 비용 때문에 소비자들의 구매가 줄어들 수 있다.

또한, 3나노를 먼저 양산한 삼성전자의 3나노 1세대는 밀도 면에서 시장의 기대치 충족에 다소 부족하다. 일부 기업들은 3나노의 밀도가 낮아 비용 대비 성능이 우수한 TSMC 5나노 구매하기를 더 원한다.

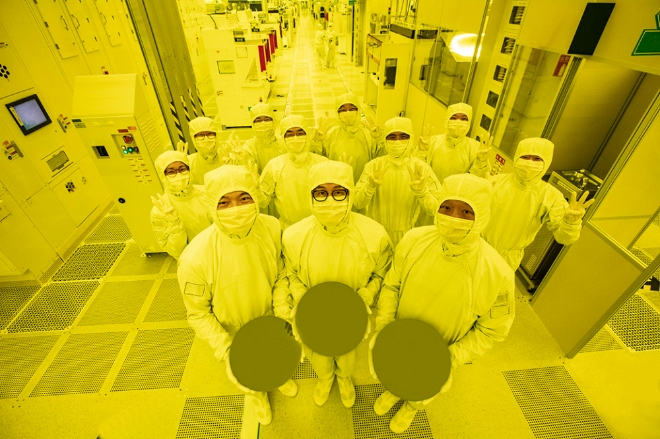

시장에서는 당초 삼성전자 3나노 1세대를 IBM(CPU), 퀄컴(스마트폰), 바이두(데이터센터)에서 구매하기로 한 것으로 알려져 있지만, 실제 계약을 체결했는지 여부는 정확하게 확인되지 않고 있다.

삼성전자의 5나노는 밀도가 126.5, 3나노 1세대가 150.6, 3나노 2세대가 194.6이다. 반면 TSMC는 5나노가 173.1, 3나노 1세대는 무려 294.3이다.

당연히 삼성전자가 할인가를 적용한다고 해도 수율이 20%에 불과한 제품을 구매하기보다는 TSMC 5나노를 구매하는 것이 더 이익이 된다. 시장에서는 삼성전자 3나노 1세대 제품화에 시기상조라는 비판도 있다.

물론 밀도는 떨어지나 성능, 전력 소비량, 면적 크기에서는 크게 개선되어 TSMC 5나노를 능가한다. 밀도와 그 외 요소 가운데 어느 것을 선택할지는 기업의 몫이다.

한편 삼성전자는 3나노 1세대 밀도에 악영향을 주는 문제를 해결하기 위해 미국의 실리콘 프로트라인 테크놀로지와 제휴해 정전기 방전 방지, 세정용 초순수 문제 해결에 나서고 있다.

현재 삼성전자는 3나노 2세대를 개발 중이며, 2023년에 생산할 계획이다. 이 칩은 전력 54%, 성능 30%, 면적 35% 개선 효과를 기대한다. 1세대에 비해 성능이 많이 개선된다.

박정한 글로벌이코노믹 기자 park@g-enews.com