수직형 옥사이드 반도체(OCTRAM) 채널 트랜지스터 8개층 적층 성공

기존 D램 대비 제조 비용 절감 및 전력 소모 획기적 감소 기대…AI 서버 시장 겨냥

기존 D램 대비 제조 비용 절감 및 전력 소모 획기적 감소 기대…AI 서버 시장 겨냥

이미지 확대보기

이미지 확대보기AI 시대에는 대량의 데이터를 처리하기 위해 더 큰 용량과 낮은 전력 소비를 갖춘 D램에 대한 수요가 급증하고 있다. 기존의 D램 기술은 메모리 셀 크기 축소의 물리적 한계에 도달하고 있어, 추가 용량을 제공하기 위한 메모리 셀의 3D 적층 연구가 절실했다.

기존 D램과 마찬가지로 적층된 메모리 셀의 트랜지스터 채널 재료로 단결정 실리콘을 사용할 경우, 제조 비용이 증가하고 메모리 셀을 새로 고치는 데 필요한 전력(리프레시 파워)이 메모리 용량에 비례하여 증가하는 문제가 있었다.

8개층 수직 적층 기술 검증

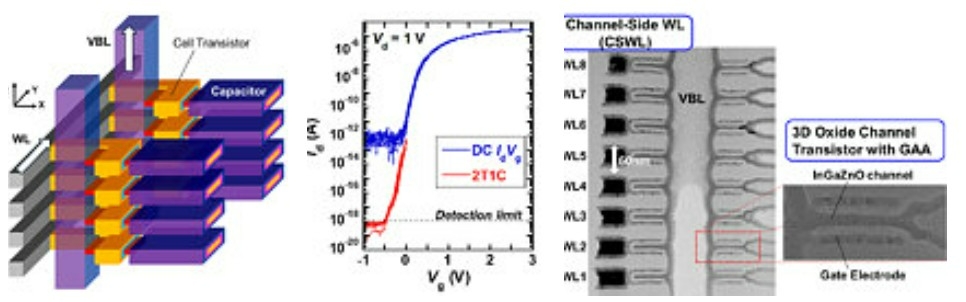

키옥시아는 이미 작년 IEDM(IEEE International Electron Devices Meeting)에서 옥사이드 반도체로 만든 수직 트랜지스터를 사용하는 OCTRAM(Oxide-Semiconductor Channel Transistor DRAM) 기술을 발표한 바 있다.

이번 IEDM 발표에서는 OCTRAM의 3D 적층을 허용하는 고도로 적층 가능한 옥사이드 반도체 채널 트랜지스터 기술을 선보였으며, 8개층으로 적층된 트랜지스터의 성공적인 작동을 검증했다.

이 새로운 기술은 성숙한 실리콘 산화물(Silicon-Oxide)과 실리콘 질화물(Silicon-Nitride) 필름을 쌓고 실리콘 질화물 영역을 옥사이드 반도체(InGaZnO)로 대체하여 수평으로 적층된 트랜지스터의 수직층을 동시에 형성한다. 키옥시아는 또한 수직 피치(Pitch)를 확장할 수 있는 새로운 3D 메모리 셀 구조를 도입했다. 이러한 제조 공정 및 구조는 메모리 셀의 3D 적층을 달성하는 데 따르는 비용 문제를 극복할 것으로 예상된다.

특히 옥사이드 반도체의 낮은 누설 전류(low off-current) 특성 덕분에 메모리 리프레시 전력을 줄일 수 있다는 점이 주목된다. 키옥시아는 대체 공정을 통해 형성된 수평 트랜지스터에서 높은 온-전류(30µA 이상)와 초저 오프-전류(1aA 미만) 능력을 시연하는 데 성공했다. 초저 오프-전류는 메모리 셀의 정보 유지 시간을 길게 하여 리프레시 주기를 줄이고 전력 소비를 획기적으로 낮춘다.

키옥시아는 앞으로도 이 기술이 실제 응용 분야에 배포될 수 있도록 연구 개발을 지속할 계획이다.

![[뉴욕증시 주간전망] 미·이란 종전 협상과 1분기 실적에 '촉각'](https://nimage.g-enews.com/phpwas/restmb_setimgmake.php?w=80&h=60&m=1&simg=2026041205402906063be84d87674118221120199.jpg)