마이크론·삼성·SK하이닉스 등 기존 메모리 제조사 역할 축소, 파운드리 공정 도입 가속화

3나노급 N3P 공정으로 전력 효율 2배 개선, 엔비디아·AMD 차세대 칩 패키징 독점 구조 강화

3나노급 N3P 공정으로 전력 효율 2배 개선, 엔비디아·AMD 차세대 칩 패키징 독점 구조 강화

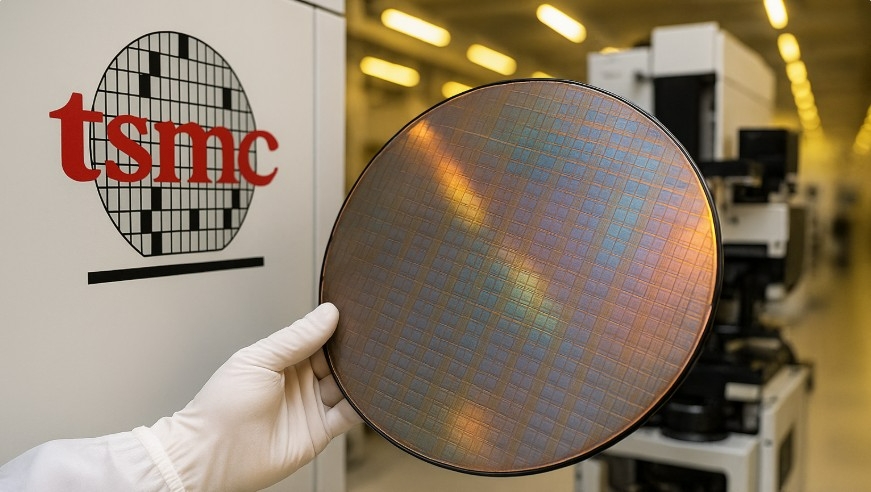

이미지 확대보기

이미지 확대보기TSMC가 차세대 고대역폭메모리(HBM)인 HBM4E 세대에서 핵심 부품인 '베이스 다이(Base Die)' 생산을 주도할 것이라는 전망이 제기됐다. 이는 기존 D램 제조사들이 주도하던 HBM 제조 공정의 핵심이 파운드리(반도체 위탁생산) 기업으로 넘어가는 중대한 구조적 변화를 시사한다. 마이크론의 최신 실적 발표와 업계 로드맵에 따르면, 향후 HBM 시장은 고객 맞춤형 제품인 'C-HBM4E'가 정식 제품군으로 부상하며 파운드리 미세 공정의 중요성이 더욱 커질 것으로 보인다.

HBM 제조 패러다임 변화, 메모리 업체에서 파운드리로

디지타임스 아시아(DIGITIMES Asia)는 1일(현지시각) 독일 하드웨어 전문 매체 하드웨어럭스(Hardwareluxx)와 마이크론의 발표를 인용해 TSMC가 HBM4E 세대의 베이스 다이 생산을 전담할 가능성이 높다고 보도했다. 마이크론은 최근 분기 실적 발표를 통해 표준형 및 맞춤형 HBM4E 메모리를 위한 베이스 로직 다이 생산을 위해 TSMC와 협력할 것이라고 공식 밝혔다.

이러한 움직임은 차세대 HBM 제조 방식의 근본적인 변화를 의미한다. 하드웨어럭스가 입수한 TSMC의 암스테르담 포럼 로드맵에 따르면, HBM4 및 HBM4E 세대부터는 삼성전자, SK하이닉스, 마이크론 등 기존 메모리 공급업체가 더 이상 베이스 다이 생산을 주도하지 않게 된다. 대신 첨단 로직 공정을 갖춘 파운드리 업체가 표준화된 베이스 다이를 제조하게 되며, 이는 멀티 다이 패키지(Multi-die Package)에 직접 통합되도록 설계된다.

N12 및 N3P 공정 도입, 전력 효율 획기적 개선

TSMC는 베이스 다이 생산에 자사의 최첨단 미세 공정을 대거 투입할 계획이다. 보도에 따르면 HBM4 베이스 다이는 TSMC의 N12 공정에서 제조될 예정이다. 이 공정을 적용할 경우 작동 전압은 기존 1.1V에서 0.8V로 낮아지며, 이를 통해 전력 효율은 약 1.5배 향상될 것으로 관측된다.

더욱 진보된 형태인 C-HBM4E의 경우, 베이스 다이 생산 공정이 N3P 노드로 전환된다. N3P는 TSMC의 3나노급 공정으로, 이를 적용 시 전압은 0.75V까지 낮아질 전망이다. 하드웨어럭스는 이러한 공정 전환을 통해 C-HBM4E의 전력 효율이 현존하는 HBM3E 대비 약 2배 수준에 달할 것이라고 분석했다.

이러한 공정 고도화는 AI 데이터센터의 핵심 난제인 전력 소모 문제를 해결할 수 있는 기술적 돌파구로 평가받는다. 미세 공정이 적용된 베이스 다이는 단순히 메모리 적층을 지지하는 역할을 넘어, 프로세서와 메모리 간의 데이터 전송 효율을 극대화하는 로직 기능을 수행하게 된다.

차세대 패키징 'CoWoS-L' 고도화, 엔비디아·AMD 칩 겨냥

새로운 버전의 CoWoS-L은 마스크(Mask) 크기 제한을 기존 대비 5.5배까지 확장할 수 있으며, 최대 12개의 HBM3E 또는 HBM4 스택을 통합할 수 있도록 지원한다. 이 기술은 2026년 출시가 예상되는 AMD의 '인스팅트(Instinct) MI450X'와 엔비디아의 차세대 가속기 '베라 루빈(Vera Rubin)' 등 고성능 제품군을 주요 타깃으로 하고 있다.

TSMC의 기술 로드맵은 여기서 멈추지 않는다. 2027년으로 계획된 후속 CoWoS-L 세대는 A16 공정을 채택하고 마스크 크기 제한을 9.5배까지 확장할 예정이다. 이를 통해 시스템 설계자들은 12개 이상의 HBM 스택을 통합한 거대 칩 설계를 구현할 수 있게 된다.

반도체 설계 및 제조의 TSMC 의존도 심화

업계 전문가들은 고성능 컴퓨팅 및 AI 칩 설계 기업들이 향후 수년간 TSMC를 배제하기 어려울 것으로 진단했다. 하드웨어럭스는 칩 설계자들이 개발 초기 단계부터 TSMC의 제조 공정 및 전자설계자동화(EDA) 도구와 깊이 연동되어 있음을 지적했다.

TSMC는 첨단 로직 노드 공정 능력 외에도 복잡한 HBM 기반 아키텍처 구현에 필수적인 멀티 칩 패키징 기술을 통합적으로 제공하고 있다. 제조와 패키징, 설계 지원을 아우르는 이러한 통합 역량은 차세대 AI 및 HPC 제품 공급망에서 TSMC의 지위를 더욱 공고히 할 것으로 분석된다.

이번 변화로 인해 메모리 반도체 시장의 전통적 강자였던 삼성전자와 SK하이닉스 등은 HBM의 핵심 부가가치가 파운드리로 이동하는 새로운 경쟁 환경에 직면하게 됐다. HBM4E 세대를 기점으로 베이스 다이 제조 주도권이 파운드리로 넘어감에 따라, 메모리 제조사들과 TSMC 간의 협력과 경쟁 구도는 더욱 복잡해질 전망이다.

박정한 글로벌이코노믹 기자 park@g-enews.com