세계 최초 'EXE:5200B' 도입으로 시간당 175장 처리…1세대 대비 생산성 대폭 강화

ASML "2027년 본격 상업 가동" 예고…삼성·TSMC 추격 따돌릴 '게임 체인저' 확보

ASML "2027년 본격 상업 가동" 예고…삼성·TSMC 추격 따돌릴 '게임 체인저' 확보

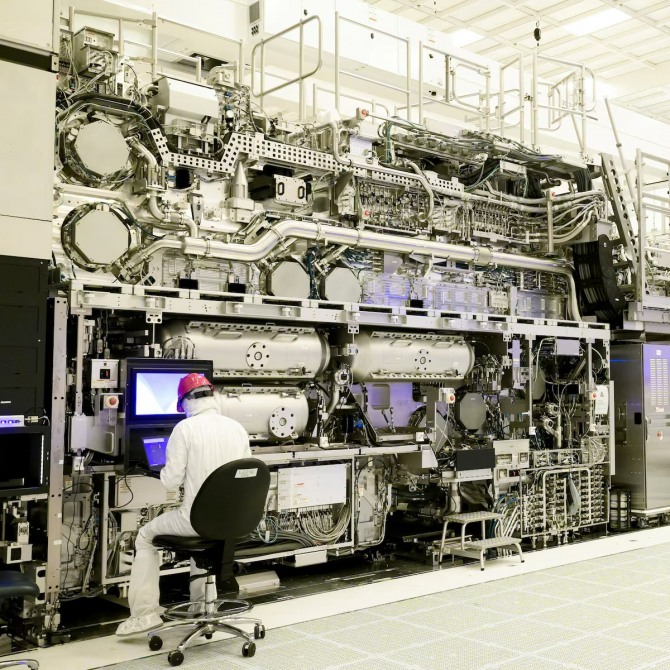

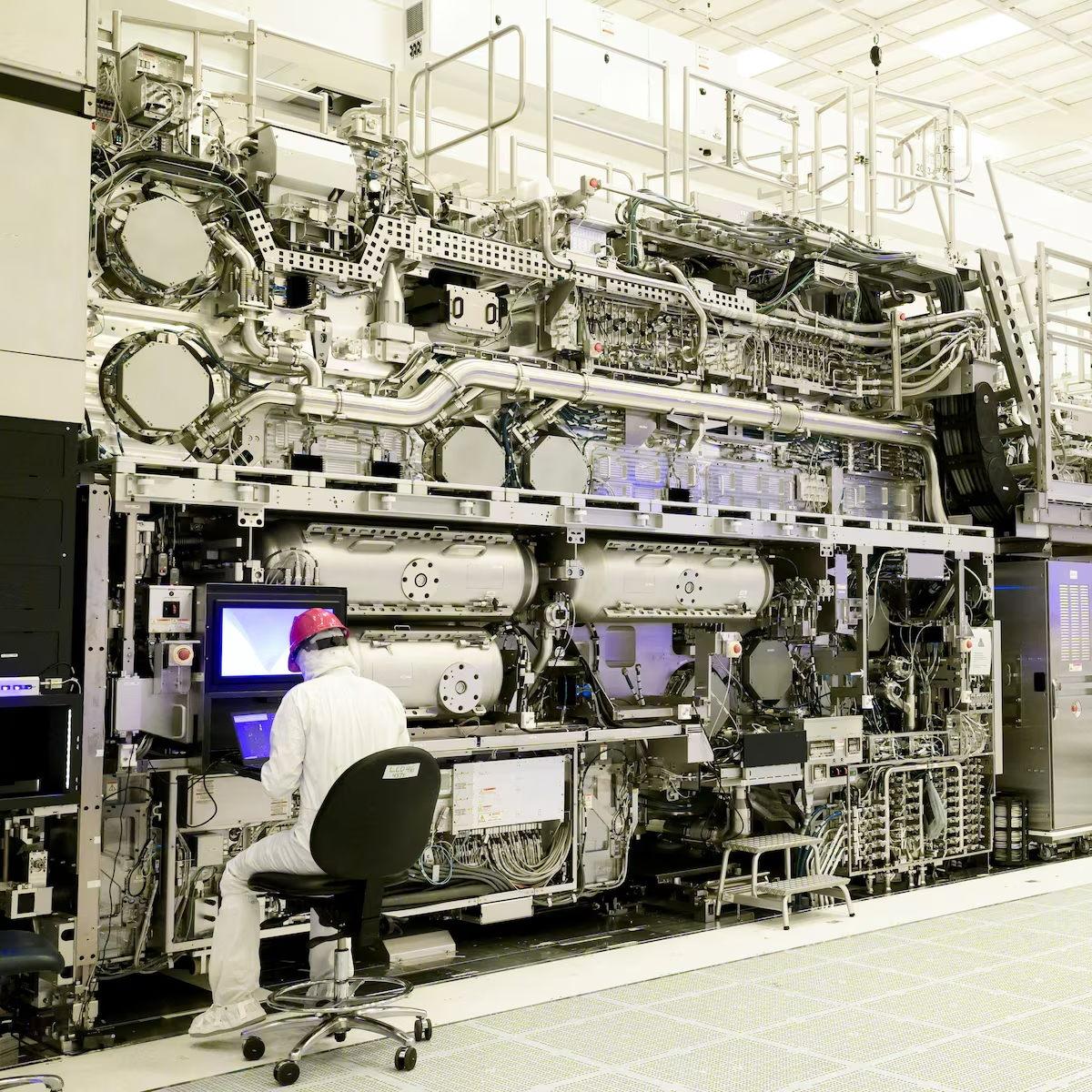

이미지 확대보기

이미지 확대보기파운드리 왕좌 탈환을 노리는 인텔의 '장비 선점' 전략이 마침내 연구실을 넘어 실제 생산 라인의 문턱에 도달했다. 네덜란드 ASML과 손잡고 세계 최초로 도입한 2세대 하이-NA EUV 장비가 인수 테스트를 통과하면서, 2나노미터(nm) 이하 초미세 공정의 '속도전'에서 인텔이 유리한 고지를 선점했다는 평가가 나온다.

인텔은 최근 자사 블로그를 통해 2세대 하이-NA(High-NA) EUV 시스템인 '트윈스캔(TWINSCAN) EXE:5200B'의 인수 테스트(Acceptance Testing)를 성공적으로 마쳤다고 발표했다. 이번 성과는 단순한 장비 도입을 넘어, 인텔 파운드리 서비스(IFS)의 제조 역량이 실제 양산 가동이 가능한 수준으로 성숙했음을 입증하는 중대한 분기점이 될 전망이다.

'시간당 175장' 생산성 확보…R&D 넘어 상업 생산 겨냥

17일(현지 시각) 블룸버그통신, 트렌드 포스 등 외신 보도에 따르면, 이번에 도입된 EXE:5200B 모델은 초기 공정 연구개발(R&D)용이었던 1세대(EXE:5000)와 달리 철저하게 '대량 양산'에 초점이 맞춰져 있다. 인텔은 이 장비를 통해 시간당 웨이퍼 처리량(Throughput)을 175장까지 끌어올렸으며, 회로를 겹쳐 쌓는 정밀도(Overlay accuracy)를 0.7nm 수준으로 미세화했다.

ASML "2027~2028년 하이-NA 본격 양산 시대"

하이-NA EUV를 활용한 실제 상업용 칩의 대량 생산 시점은 2027년경이 될 것으로 보인다. 크리스토프 푸케(Christophe Fouquet) ASML CEO는 블룸버그와의 인터뷰에서 "하이-NA 시스템을 활용한 대량 제조는 2027년에서 2028년 사이에 본격화될 것"이라며, "2026년까지 고객사들과 협력해 장비 가동 중단 시간을 최소화하는 최적화 작업을 이어갈 계획"이라고 밝혔다.

푸케 CEO는 인텔을 비롯한 선도적 고객사들이 현재 새 시스템을 통해 더욱 진보된 AI 애플리케이션용 칩 생산 가능성을 확인하고 있다고 강조했다. 그는 "이미 시연된 노광 개선 효과와 이미지 해상도가 매우 우수하며, 이제는 시스템의 성숙도를 최종 점검하는 단계"라고 덧붙였다.

인텔은 이번 2세대 장비의 인수 테스트 완료를 기점으로 '포스트 2나노' 공정으로 불리는 14A(1.4나노급) 공정 도입에 박차를 가할 계획이다. 한편 ASML은 차세대 기술인 '하이퍼-NA(Hyper NA)' 연구에도 이미 착수했다고 밝혀, 글로벌 반도체 장비 주도권을 둘러싼 인텔과 ASML의 밀월 관계는 향후 10년 이상 지속될 것으로 보인다.

![[엔비디아 GTC 2026] 'AI 추론 칩' 공개로 주가 반등 시동 걸리나](https://nimage.g-enews.com/phpwas/restmb_setimgmake.php?w=80&h=60&m=1&simg=2026031418273707380fbbec65dfb211211153121.jpg)