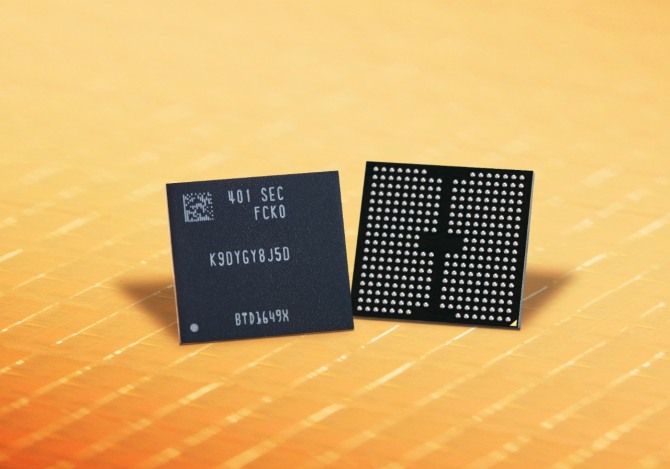

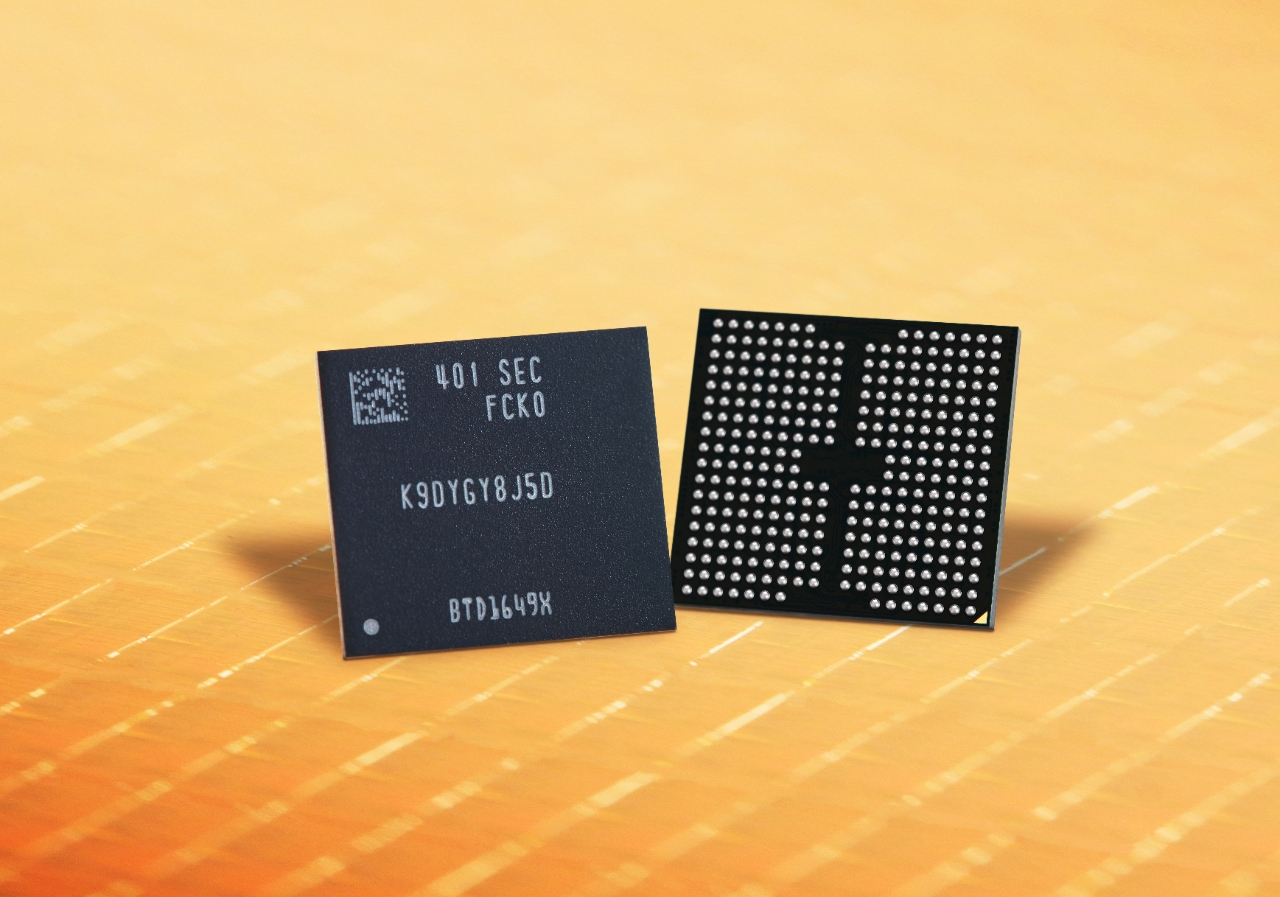

셀 면적 줄이고 간섭현상 줄여 이전 세대 대비 비트 밀도 1.5배 증가

이미지 확대보기

이미지 확대보기TCL는 하나의 셀에 3bit(비트)의 데이터를 기록할 수 있는 구조로 삼성전자는 업계 최소 크기의 셀과 최소 몰드 두께를 구현해 '1Tb TLC 9세대 V낸드'의 비트 밀도를 이전 세대 대비 약 1.5배 증가시켰다.

더미 채널 홀 제거 기술을 적용해 셀의 평면적을 줄이고 셀의 크기를 줄이면서 생기는 간섭현상을 제어하기 위해 셀 간섭 회피 기술, 셀 수명 연장 기술을 적용해 제품 품질과 신뢰성도 높였다.

특히 이번 제품은 더블 스택 구조로 구현할 수 있는 최고 단수 제품이다. '채널 홀 에칭' 기술을 통해 한 번에 업계 최대 단수를 뚫는 공정 혁신을 이뤄 생산성이 향상된 것이 특징이다. '채널 홀 에칭'이란 몰드층을 순차적으로 적층한 다음 한 번에 전자가 이동하는 홀(채널 홀)을 만드는 기술이다. 적층 단수가 높아져 한 번에 많이 뚫을수록 생산효율 또한 증가하기 때문에 정교하고 고도화된 기술력이 요구된다.

저전력 설계 기술을 탑재해 소비전력도 이전 세대 제품 대비 약 10% 개선됐다.

삼성전자는 'TLC 9세대 V낸드'에 이어 올 하반기 '쿼드레벨셀(QLC) 9세대 V낸드'도 양산해 인공지능(AI) 시대에 요구되는 고용량·고성능 낸드플래시 개발에 박차를 가할 계획이다.

허성회 삼성전자 메모리사업부 플래시(Flash)개발실장(부사장)은 "낸드플래시 제품의 세대가 진화할수록 고용량·고성능 제품에 대한 고객의 니즈가 높아지고 있어 극한의 기술 혁신을 통해 생산성과 제품 경쟁력을 높였다"며 "9세대 V낸드를 통해 AI 시대에 대응하는 초고속·초고용량 SSD 시장을 선도해 나갈 것"이라고 밝혔다.

장용석 글로벌이코노믹 기자 jangys@g-enews.com

![[엔비디아 GTC 2026] 'AI 추론 칩' 공개로 주가 반등 시동 걸리나](https://nimage.g-enews.com/phpwas/restmb_setimgmake.php?w=80&h=60&m=1&simg=2026031418273707380fbbec65dfb211211153121.jpg)