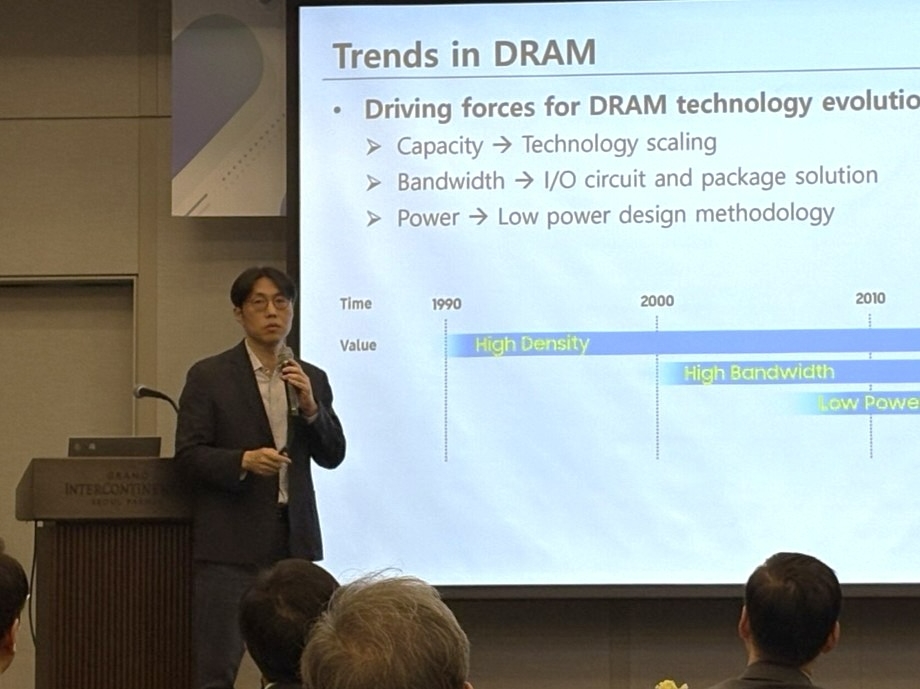

'AI 시대 D램' 주제 강연

HBM 한계 다다른 이후 대비

기존 기술 혼용해 사용성↑ 필요

HBM 한계 다다른 이후 대비

기존 기술 혼용해 사용성↑ 필요

이미지 확대보기

이미지 확대보기손교민 삼성전자 D램설계팀 마스터는 이날 반도체공학회가 서울 강남구 그랜드 인터컨티넨탈 서울 파르나스에서 개최한 인공지능반도체포럼 조찬강연회의 연사로 나서 ‘AI 시대를 위한 D램 솔루션’을 주제로 강연했다. 손 마스터는 삼성전자의 미래 설계회로 분야에서 연구개발을 맡아왔고, 2020년 삼성전자 HBM2E(3세대) 플래시볼트를 개발했다.

이 자리에서 손 마스터는 D램의 성능을 최대한 끌어올리기 위한 솔루션으로 HBM뿐만 아니라 PIM과 CXL을 언급했다. PIM은 D램 간 데이터를 주고받는 HBM과 달리 한 메모리 안에서 데이터를 처리할 수 있게 설계한 메모리다. CXL은 프로세서와 장치 간에 데이터 흐름을 더 효율적으로 만들기 위해 일관된 프로토콜 체계를 갖춘 기술이다.

컴퓨터가 작동하는(컴퓨팅) 체계를 유지하면서 전체 메모리 성능을 끌어올리기 위해 HBM과 PIM을 혼합 사용하는 방안이 필요하다고 손 마스터는 설명했다. 메모리들 사이에 있는 데이터 전송 공간인 ‘대역폭’을 고도화하고 D램 간격을 최소화하는 식으로 설계해 성능을 끌어올리는 HBM이 아직 유일한 솔루션이기 때문이다. 삼성전자는 지난 2021년 HBM-PIM을 세계 최초로 개발한 경험을 보유하고 있다.

또 다른 차세대 메모리인 CXL에 관해서는 데이터 저장용량을 획기적으로 늘린 낸드플래시 기술과 혼합하는 ‘하이브리드 구조’를 언급했다. CXL에 탑재하는 D램 수를 획기적으로 늘리려면 메모리 장벽을 넘기 위해 더 많은 시간과 자원을 투자해야 하기 때문이다.

손 마스터는 “용량을 늘리고 싶어 낸드플래시를 쓸 때 D램에서 낸드로 데이터를 옮기는 시간이 너무 길다는 단점을 피하기 위해 D램을 다량으로 탑재하자는 아이디어”라면서 “CXL을 박스 형태로 모은 거대 D램이나, 낸드랑 섞어서 하이브리드 구조를 띠는 데이터 전송 속도가 빠른 D램과 저장용량이 큰 낸드플래시를 조합한 하이브리드 구조도 생각해볼 수 있다”고 언급했다.

정승현 글로벌이코노믹 기자 jrn72benec@g-enews.com