美 EUV 장비 제재 직격탄…DUV 멀티패터닝 공정 한계 드러내

화웨이 AI 칩 생산비용 급등…TSMC와 기술 격차 심화

화웨이 AI 칩 생산비용 급등…TSMC와 기술 격차 심화

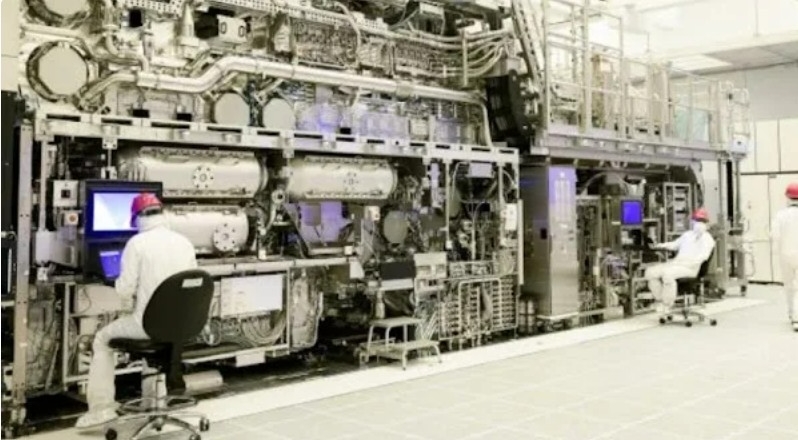

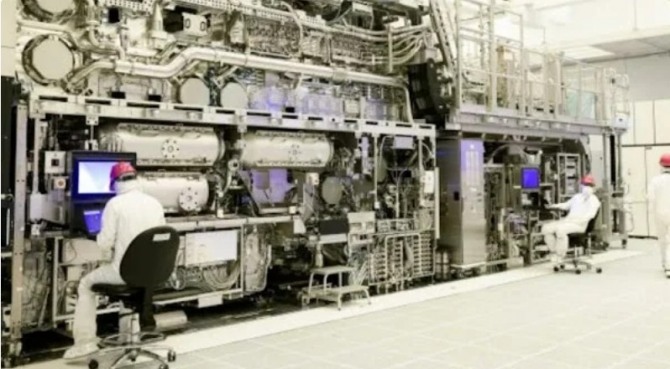

이미지 확대보기

이미지 확대보기중국 최대 파운드리(반도체 위탁생산) 업체인 SMIC의 인공지능(AI) 칩 생산 계획에 '빨간불'이 켜졌다. 미국의 첨단 장비 제재 때문에 핵심 공정 수율이 30% 수준에 머무르면서, 글로벌 투자은행 모건스탠리가 SMIC의 AI 칩 관련 매출 전망치를 사실상 반 토막 냈다. 중국의 '반도체 굴기'가 기술 한계와 외부 제재라는 암초에 부딪혔다.

SMIC가 직면한 가장 큰 문제는 AI 그래픽처리장치(GPU)의 낮은 수율이다. 7일(현지시각) 모건스탠리 보고서에 따르면 SMIC의 AI GPU 수율은 2025년 말까지 30%에 그칠 전망이다. 이는 경쟁사인 대만 TSMC의 5나노 공정 수율이 90%를 웃도는 것과 비교하면 매우 심각한 수준이다.

이처럼 수율이 낮은 근본적인 원인으로는 미국의 제재가 꼽힌다. SMIC는 네덜란드 ASML로부터 최첨단 극자외선(EUV) 노광 장비를 확보하지 못해 구형 심자외선(DUV) 장비에 의존한다. DUV 장비로 7나노미터(nm)급 미세 공정을 구현하려면, 회로를 여러 번 반복해서 그리는 '멀티패터닝' 기술을 사용해야 한다. 이 공정은 기술적으로 복잡하고 생산 단계를 늘려 비용 상승과 수율 하락을 부른다. 여기에 서방 제조사 장비의 정밀 유지보수 기술 부족 문제까지 겹쳤다. 실제로 SMIC는 2025년 2분기 장비 점검 실패로 약 6%의 수율과 생산량 손실을 봤다.

◇ 직격탄 맞은 화웨이, AI 칩 생산비 '눈덩이'

◇ 매출 전망 '반 토막'…커지는 기술 격차

모건스탠리는 SMIC의 AI 칩 부문 매출 전망치를 대폭 낮췄다. 2025년 매출 전망치는 기존 1억 4600만 위안(약 284억 원)에서 5850만 위안(약 113억 원)으로, 2026년은 2억 1200만 위안(약 413억 원)에서 9400만 위안(약 183억 원)으로, 2027년은 2억 8650만 위안(약 558억 원)에서 1억 3600만 위안(약 264억 원)으로 각각 50% 가까이 줄였다.

보고서는 SMIC의 910B 칩 수율이 2027년에 70%까지 회복될 것으로 내다봤지만, 단기적인 생산 차질과 재무 타격은 피하기 어렵다. 이에 SMIC은 긴급히 3000만~7500만 달러(약 416억~1041억 원) 규모의 연구개발(R&D) 예산을 투입하고 조기에 생산 설비를 늘리는 등 수율 확보에 사활을 걸고 있지만, 삼성전자나 TSMC와의 기술 격차는 여전하다는 평가가 나오고 있다.

박정한 글로벌이코노믹 기자 park@g-enews.com