지난해 생산한 기판 면적이 축구 경기장 100개 면적

기판 핵심 기술은 '미세 가공 기술', '미세회로 구현'

기판 핵심 기술은 '미세 가공 기술', '미세회로 구현'

이미지 확대보기

이미지 확대보기"내가 놓친 이물, 불량 되어 돌아온다“

삼성전기 반도체 패키지 기판(FCBGA) 제조 공장 계단, 벽마다 붙어 있는 문구다. 이토록 이물, 불량에 집중하는 까닭은 무엇일까?

답은 수율(투입 수에 대한 완성된 양품의 비율)에 있다. 최근 대형화가 추세가 되면서 수율이 낮아질 수밖에 없다. 판넬(투입단위) 하나당 기판의 개수가 줄어들기 때문이다.

이렇게 되면 100개 중 5개가 불량이면 95%의 수율이지만 10개 중 1개만 불량이어도 수율이 10%씩 떨어지게 된다.

과거보다 2~3배 낮은 수율 자체로 리스크가 크기 때문에 이물관리가 철저해지고 기판 하나하나가 매우 중요해진 것이다.

FCBGA가 이토록 뜨는 산업이 된 것도 공급이 확 줄어들었기 때문이다. 기판이 없으면 반도체를 제작하기 어렵기에 반도체업체들은 투자를 제안하거나 가격을 올려서라도 물량을 확보하기 위해 동분서주하고 있지만, 이러한 공급 부족 상황은 단기간 해소되지 않을 전망이다.

이미지 확대보기

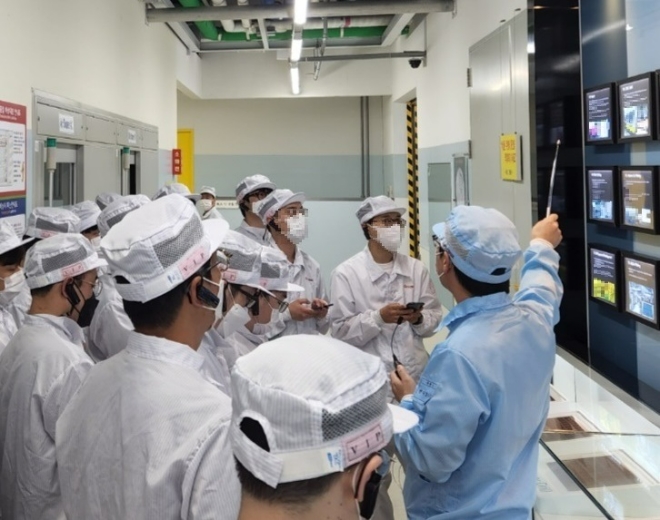

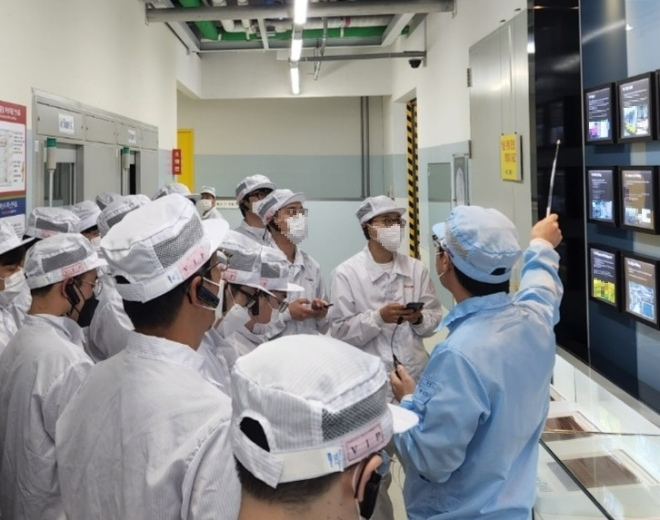

이미지 확대보기그렇기에 반도체 기판을 생산하는 삼성전기 부산사업장 FCB동에 입장할 때는 까다로운 절차가 필요했다.

우선 로션, 스킨 외 메이크업은 물론, 선크림도 바르지 않아야 했다. 방진복, 모자, 장갑, 신발을 모두 갈아신고 갈아신은 실내화마저 물로 씻은 뒤 에어샤워까지 끝마쳐야 입장이 가능했다.

삼성전기가 지난 한 해 생산한 반도체 패키지 기판의 면적은 70만3000㎡(제곱미터)로 축구 경기장 100개 면적의 규모와 맞먹는 규모다. 이러한 거대 물량을 소화하기 위해 설비 가동률은 거의 100% 수준을 유지하고 있다.

하지만 이러한 많은 물량에 비해 사람은 적어 보였다. 내부엔 사람보다 거대한 설비와 기계 소음들이 가득 채웠다. 서너 걸음만 떨어져 있는 근거리에서도 대화가 힘들 정도였다.

이렇게 사람보다 기계가 많은 것은 반도체 패키지 공정이 사람이 직접 할 수 없을 만큼 미세한 공정이기 때문이다. 반자동 시스템이기에 근로자는 각 공정이 끝날 때마다 제품을 투입하고 설비관리하는 등의 작업을 한다.

이미지 확대보기

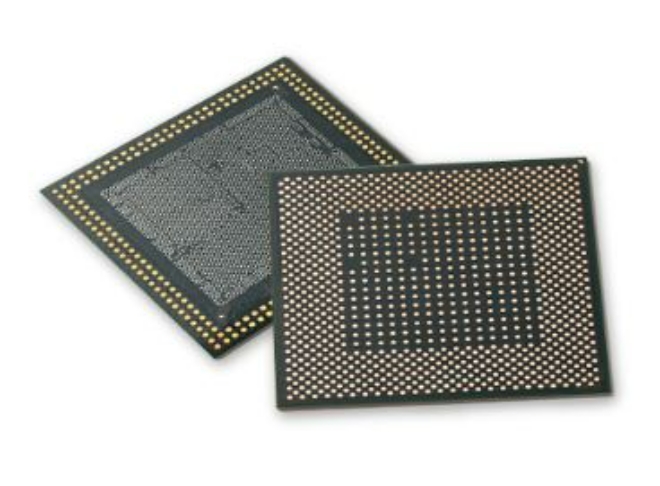

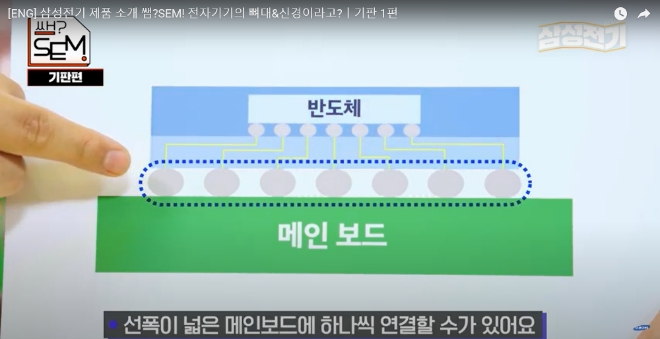

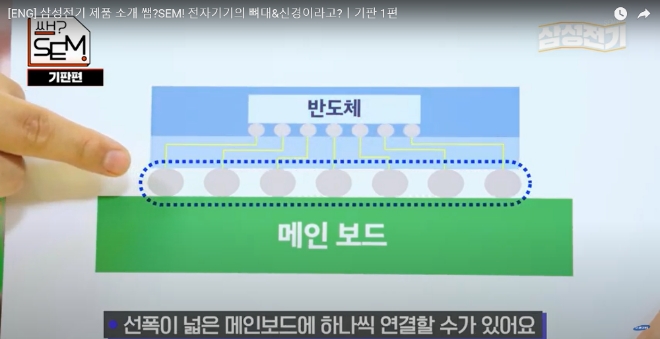

이미지 확대보기패키지기판은 반도체와 메인 기판 간 전기적 신호를 전달하고, 반도체를 외부의 충격 등으로부터 보호해 주는 역할을 한다.

반도체 칩은 메인 기판과 서로 연결돼야 하는데 메인 기판의 회로는 반도체보다 미세하게 만들기가 불가능하다. 반도체 칩의 단자 사이 간격은 100um(마이크로미터)로 A4 두께 수준인 것에 비해, 메인 기판의 단자 사이 간격은 약 350um로 4배 정도 차이가 난다.

따라서, 반도체 칩과 메인 기판 사이를 연결해 주는 다리 역할이 필요한데 이것이 패키지 기판이다. 패키지 기판이 선폭이 넓은 메인보드에 반도체 단자를 하나씩 연결하는데 이를 '재배선'한다고 한다. 이 재배선이 반도체 패키지 기판의 가장 중요한 역할이다.

패키지기판을 만드는 데 필요한 핵심 기술은 '미세 가공 기술' 과 '미세회로 구현' 이다.

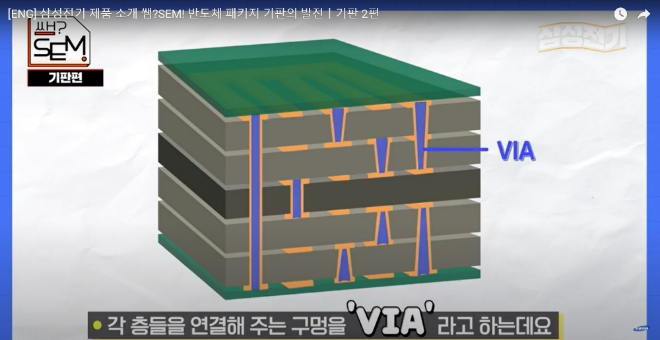

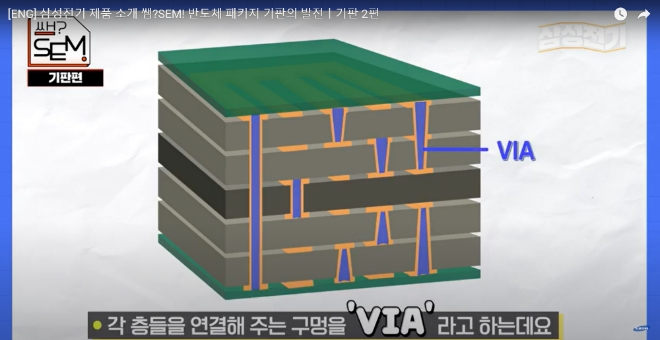

반도체 기판은 신호 전달에 필요한 길인 회로가 많아지는데 한정된 면적 안에 많은 회로를 만들기 위해 여러 층으로 만든다. 이때 층간을 연결하는 구멍을 뚫는데 이 구멍을 비아(Via)라고 한다. 이때 공정은 레이저로 구멍 뚫어 레이저 드릴(Laser drilling)이라 부른다.

일반적으로 80um 크기의 면적 안에 50um 수준의 구멍을 오차 없이 정확히 뚫어야 하기에 정교한 가공 기술력이 필요하다. 이 말은 A4용지의 절반 수준의 구멍을 일정한 간격으로 내야 한다는 뜻이다.

이미지 확대보기

이미지 확대보기고객사가 요구하는 비아 사이즈는 작아지는 추세이며 반도체 수준의 비아를 개발 중이다. 삼성전기도 A4용지 두께의 10분의 1인 10um 수준의 비아를 구현할 수 있지만, 아직 상용화 단계는 아니다.

반도체 기판은 미리 만들어 놓지는 않고 고객의 주문을 받은 후 생산한다. 아직 안정적으로 수율이 나오지 않지만 앞으로 고객사의 요구를 폭넓게 주문을 받을 수 있도록 개발 중이다.

반도체 기판 패키지는 백수십 가지의 복잡한 과정을 거치지만 간략하게 보면 아래와 같은 공정이 기본적으로 들어간다.

재료 투입→구멍 뚫는 공정(Laser drilling)→무전해 동도금(E'less Cu plating)→DF 도포, 노광, 현상(Dry film image)→동도금(Cu plating)→DF박리(DF strippong)→플래시 에칭(Flash etching)

전기신호가 지나가는 길인 회로는 부품의 단자가 많아지고 연결해야 할 신호가 많아지면서 회로 선폭과 간격도 미세화되고 있다. 제작 과정은 원하는 회로 두께만큼 도금 후 남는 부분을 코팅한 다음 화학 작용(에칭)을 통해 필요한 회로만 형성하게 된다.

일반적으로 회로 폭과 회로 간 간격이 8~10um 수준의 얇은 선 폭을 구현해야 하는 어려운 기술이다. 최근에는 반도체 입출력 단자 수가 증가하면서 더 미세한 회로 구현이 필요로 하는데 삼성전기는 머리카락 두께의 1/40인 3um 수준의 회로선 폭을 구현할 수 있는 기술력을 보유하고 있다.

부산=정진주 글로벌이코노믹 기자 pearl99@g-enews.com