1c D램과 4나노 베이스 다이로 재설계 없이 적기에 수율·성능 확보

코어 다이 저전력 설계·전력 분배 최적화…전력효율·발열 개선

코어 다이 저전력 설계·전력 분배 최적화…전력효율·발열 개선

이미지 확대보기

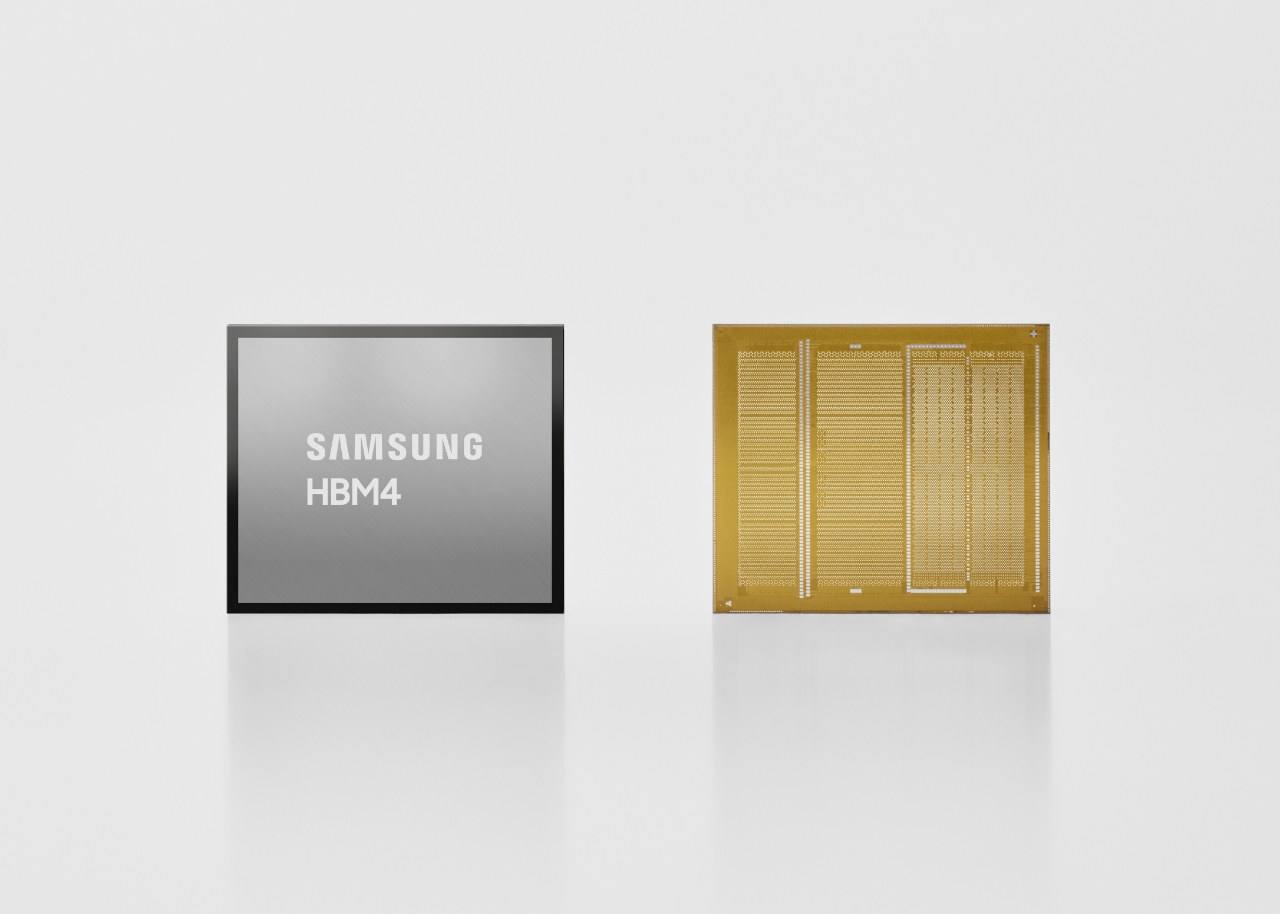

이미지 확대보기삼성전자는 12일 최선단 공정 1c D램(10나노급 6세대)을 적용한 HBM4를 양산 출하했다고 12일 밝혔다. 삼성전자는 HBM4 기술 경쟁력 강화를 위해 1c D램을 적용하고, 베이스 다이의 특성을 고려해 성능과 전력 효율 면에서 유리한 4나노(nm, 10억분의 1m) 공정을 적용했다.

그 결과 삼성전자 HBM4는 국제반도체표준협의기구(JEDEC) 업계 표준인 8Gbps를 약 46% 웃도는 11.7Gbps의 동작 속도를 안정적으로 확보했다. 삼성전자는 HBM4 개발 착수 단계부터 JEDEC 기준을 웃도는 성능 목표를 설정하고 개발을 추진해왔다.

11.7Gbps의 속도는 전작인 5세대 고대역폭메모리(HBM3E)의 최대 핀 속도인 9.6Gbps 대비 약 1.22배 향상된 수치로 최대 13Gbps까지 구현이 가능해 인공지능(AI) 모델 규모가 커질수록 심화되는 데이터 병목을 효과적으로 해소할 것으로 기대된다.

삼성전자의 HBM4는 12단 적층 기술을 통해 24~36GB의 용량을 제공하고 고객사의 제품 일정에 맞춰 16단 적층 기술을 적용해 최대 48GB까지 용량을 확장할 계획이다.

삼성전자는 데이터 전송 인풋/아웃풋(I/O) 핀 수가 1024개에서 2048개로 확대됨에 따라 발생하는 전력 소모와 열 집중 문제를 해결하기 위해 코어 다이에 저전력 설계 기술을 적용했다. 실리콘 관통전극(TSV) 데이터 송수신 저전압 설계 기술 적용과 전력 분배 네트워크(PDN) 최적화를 통해 전 세대 대비 에너지 효율을 약 40% 개선했고, 열 저항 특성은 약 10%, 방열 특성은 약 30% 향상시켰다.

삼성전자의 HBM4 출하 뒤에는 세계에서 유일하게 △로직 △메모리 △파운드리(반도체 수탁생산) △패키징까지 아우르는 '원스톱 솔루션'을 제공할 수 있는 경쟁력이 자리하고 있다. 삼성전자는 자체적으로 보유한 파운드리 공정과 HBM 설계 간의 긴밀한 DTCO 협업을 통해 품질과 수율을 동시에 확보한 최고 수준의 HBM을 지속적으로 개발해 나갈 계획이다.

삼성전자가 선단 패키징 역량을 보유하고 있다는 점도 장점이다. 이를 통해 삼성전자는 공급망 리스크를 최소화하는 한편 생산 리드타임을 단축한다는 계획이다.

생산능력 확대 속도

이미지 확대보기

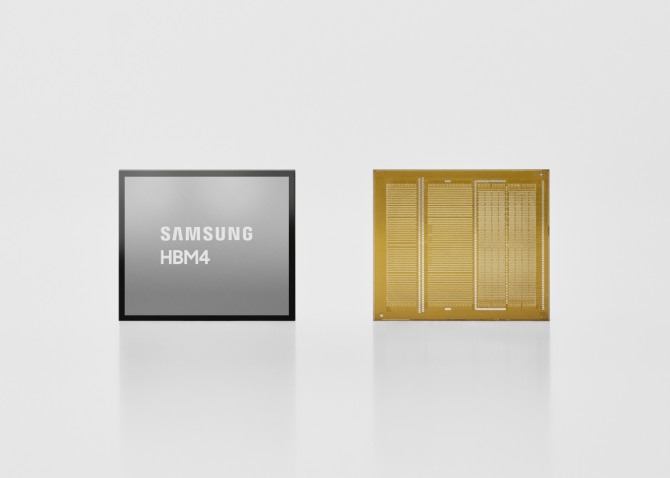

이미지 확대보기현재 삼성전자는 글로벌 주요 그래픽처리장치(GPU)와 자체 칩을 설계·개발하는 차세대 주문형 반도체(ASIC) 기반 하이퍼스케일러 고객사들로부터 HBM 공급 협력 요청을 지속적으로 받고 있다. 향후 이들과의 기술 협력을 더욱 확대해 나갈 방침이다.

이에 따라 삼성전자는 올해 HBM 매출이 지난해 대비 3배 이상 증가할 것으로 보고, HBM4 생산 능력을 선제적으로 확대하고 있다.

삼성전자는 업계 최대 수준의 D램 생산능력과 선제적인 인프라 투자를 통해 확보해온 클린룸을 기반으로 HBM 수요가 확대될 경우에도 단기간 내 유연하게 대응할 수 있는 생산 역량도 갖추고 있다.

2028년부터 본격 가동될 평택사업장 2단지 5라인은 HBM 생산의 핵심 거점으로 활용될 예정으로 AI·데이터센터 중심의 중장기 수요 확대 국면에서도 안정적인 공급 대응 역량을 지속적으로 확보해 나갈 예정이다.

삼성전자는 HBM4에 이어 HBM4E도 준비 중으로 2026년 하반기에 샘플을 출하할 계획이다. 커스텀 HBM도 2027년부터 고객사별 요구에 맞춰 순차 샘플링을 시작할 계획이다.

황상준 삼성전자 메모리개발담당 부사장은 "삼성전자 HBM4는 그전에 검증된 공정을 적용하던 전례를 깨고 1c D램과 파운드리 4나노(nm)와 같은 최선단 공정을 적용했다"면서 "공정 경쟁력과 설계 개선을 통해 성능 확장을 위한 여력을 충분히 확보함으로써 고객의 성능 상향 요구를 적기에 충족할 수 있었다"고 설명했다.

장용석 글로벌이코노믹 기자 jangys@g-enews.com